### Introduction

| CONTENTS |   |                                                                                                |  |  |

|----------|---|------------------------------------------------------------------------------------------------|--|--|

| Part-1   | : | VLSI Design Flow 1-2F to 1-4F                                                                  |  |  |

| Part-2   | : | General Design Methodologies : 1-4F to 1-5F<br>Critical Path and Worst Case<br>Timing Analysis |  |  |

| Part-3   | : | Overview of Design Hierarchy 1-5F to 1-6F                                                      |  |  |

| Part-4   | : | Layers of Abstraction, <b>1-6F to 1-9F</b><br>Integration Density<br>and Moore's Law           |  |  |

| Part-5   | : | VLSI Design Styles 1-9F to 1-13F                                                               |  |  |

| Part-6   | : | Packaging 1-13F to 1-14F                                                                       |  |  |

| Part-7   | : | CMOS Logic 1-14F to 1-21F                                                                      |  |  |

| Part-8   | : | Propagation Delay Definitions 1-22F to 1-22F                                                   |  |  |

| Part-9   | : | Sheet Resistance 1-22F to 1-23F                                                                |  |  |

1-1 F (EC-Sem-7)

1-2F (EC-Sem-7)

Introduction

#### PART-1

VLSI Design Flow.

#### VLSI Design

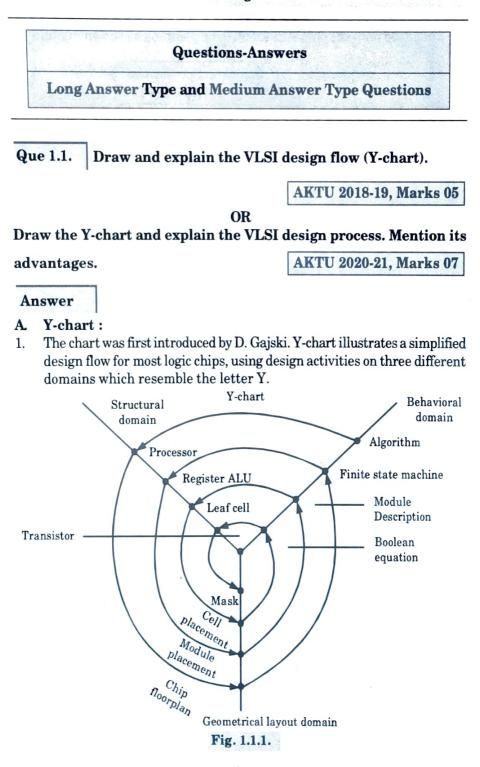

- 2. The Y-chart consists of three domains of representation namely behavioral, structural and geometrical layout domain.

- 3. The design flow starts from algorithm that describes the behavior of the target chip.

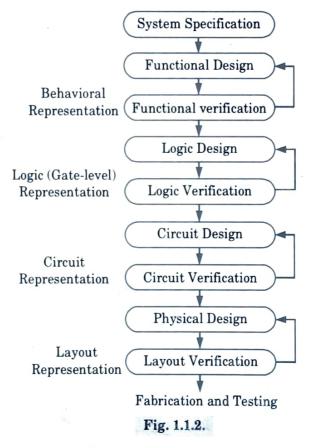

- 4. The corresponding architecture of the processor is then defined. It is mapped onto the chip surface by floor-planning as shown in Fig. 1.1.2.

- 5. The next design evolution defines FSM implemented with registers and ALU. These modules are then geometrically placed onto chip surface using CAD tools.

- 6. The third evolution starts with behavioral module description. Individual modules are then implemented with leaf cells. Logic gates (leaf cells) can be placed by using a cell placement and routing program.

- 7. The last stage involves implementation of leaf and mask generation. Fig. 1.1.2 below provides a more simplified view of the VLSI design flow.

- 8. Note that the verification of design plays a very important role in every step during this process.

- 9. The failure of design during verification causes expensive re-design at latter stage and results in increased time to market.

#### 1-4 F (EC-Sem-7)

10. Although top-down design flow appeals for design process, but in reality there is no uni-directional to<sub>1</sub>-down design flow. Both top-down and bottom-up approaches have to be combined for a successful design.

#### **B.** Advantages :

- 1. Reduced size for circuits.

- 2. Increased cost-effectiveness for devices.

- 3. Improved performance in terms of the operating speed of circuits.

- 4. Requires less power than discrete components.

- 5. Higher device reliability.

- 6. Requires less space and promotes miniaturization.

#### PART-2

General Design Methodologies : Critical Path and Worst Case Timing Analysis.

#### **Questions-Answers**

Long Answer Type and Medium Answer Type Questions

#### Que 1.2.

Explain critical path with example.

#### Answer

#### A. Critical path :

- 1. The critical path is defined as the path between an input and an output with the maximum delay. Once the circuit timing has been computed, the critical path can easily be found by using a traceback method.

- 2. Critical paths are timing-sensitive functional paths, because of the timing of these paths is critical, no additional gates are allowed to be added to the path, to prevent increasing the delay of the critical path.

#### B. Example:

- 1. The STA (Static Timing Analysis) tool will add the delay contributed from all the logic connecting the Q output of one flip-flop to the D input of the next and then compare it against the defined clock period of the CLK pins. This should be strictly less than the clock period defined for that clock.

- 2. If the delay is less than the clock period, then the path meets timing. If it is greater, then the path fails timing.

- 3. The critical path is the path out of all the possible paths that either exceeds its constraint by the largest amount, or if all paths pass, then the one that comes closest of failing.

#### VLSI Design

#### Que 1.3. Write a short note on worst case timing analysis.

#### Answer

- 1. The worst-case timing analysis (WCTA) portion of WCCA analyzes the timing of digital devices and signal paths under worst-case conditions.

- 2. It usually accompanies many other assessments such as decoupling, signal integrity, and DC compatibility.

- 3. For WCTA, Timing Designer analyzes the results of the Printed-Circuit Board (PCB) propagation delay, extracted from HyperLynx and the static timing numbers of the FPGA or ASIC.

- 4. Through WCTA, setup and hold time violations can be analyzed.

#### PART-3

Overview of Design Hierarchy.

Long Answer Type and Medium Answer Type Questions

Que 1.4. Write a short note on design hierarchy, regularity, modularity and locality.

OR

Explain the concept of design hierarchy with the help of example.

AKTU 2017-18, Marks 10

#### Answer

#### A. Design hierarchy :

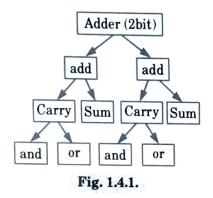

- 1. The use of hierarchy involves dividing module into sub-modules until the complexity of the smaller parts becomes manageable.

- 2. Similarly, the design of VLSI chip can be represented in three domains.

- 3. It is important for the simplicity of design that the hierarchies in different domains be mapped. Fig. 1.4.1 shows the structural decomposition of a CMOS 2 bit adder into its components.

- 4. Adder can be decomposed into 1 bit adders, separate carry and sum circuits and individual logic gates.

- 5. The above partitioning provides a valuable guidance for realization of these blocks on the chip. The approximate shape and area of each sub-module should be estimated in order to provide a useful floor place.

#### 1-6 F (EC-Sem-7)

Introduction

#### B. Regularity :

- 1. Regularity means that the hierarchical decomposition of a large system should result in simple as well as similar blocks as much as possible.

- 2. Regularity can exist at all level of abstraction. For example, design of array structures consisting of identical cells at transistor level and at gate level.

- 3. If the designer has a small library of basic building blocks, a number of different functions can be constructed by using this principle.

- 4. Regularity usually reduces the number of different modules that need to be designed and verified, at all levels of abstraction.

#### C. Modularity:

- 1. Modularity in design means that the various functional blocks which make up the large system must have well-defined functions and interfaces.

- 2. Each block or module can be designed independent from each other such flexibility is provided by modularity. All the blocks can be combined easily at the end of the design process to form the large system.

- 3. The concepts of modularity enable the parallel process during the design.

#### D. Locality:

- 1. The concept of locality ensures that connections between module to module are mostly between neighbouring modules, avoiding distance connections as much as possible.

- 2. During interfacing each module in the system, make sure that the internals of each module becomes unimportant to the exterior module.

- 3. Far-interconnections can be avoided as they provide long delays in the system. All the time-delays operations should be performed locally, without the need to access far placed modules.

PART-4

Layers of Abstraction, Integration Density and Moore's Law.

VLSI Design

#### **Questions-Answers**

Long Answer Type and Medium Answer Type Questions

#### Que 1.5. What are the levels of abstraction ? Explain.

#### Answer

#### The levels (layers) of abstraction are :

- i. Behavioral or algorithmic level : This is the highest level of abstraction. A module can be implemented in terms of the design algorithm. The designer no need to have any knowledge of hardware implementation.

- ii. Data flow level : In this level, the module is designed by specifying the data flow. Designer must how data flows between various registers of the design.

- iii. Gate level : The module is implemented in terms of logic gates and interconnections between these gates. Designer should know the gate-level diagram of the design.

- iv. Switch level: This is the lowest level of abstraction. The design is implemented using switches/transistors. Designer requires the knowledge of switch-level implementation details.

### Que 1.6. What do you mean by high integration density? Also explain the different scales of integration ?

#### Answer

A. High integration density : A high integration density means a large number of components in a small area.

#### B. Different scales of integration :

Depending upon the number of active devices per chip, there are different levels of integration :

i. SSI:

When the active devices per chip are less than 100, then it is referred as small scale integration (SSI). Most of the SSI chips use integrated resistors, diodes and bipolar transistors.

#### ii. MSI:

When the count of active devices per chip is between 100 and 1000, then it is referred as medium scale integration (MSI). In most of the MSI chips, BJTs and enhancement mode MOSFETs are integrated.

#### 1-8F (EC-Sem-7)

#### iii. LSI:

In large scale integration (LSI), the number of active devices per chip ranges between 1000 and 100,000. In general, LSI chips use MOS transistors; as it requires less number of steps for integration. Thus more number of components can be produced on the chip with MOS transistors than with the bipolar transistors.

#### iv. VLSI:

When the active devices per chip are over hundreds of thousands, then it is referred as very large scale integration (VLSI). Almost all modern chips employ VLSI technique.

#### v. ULSI:

Recently a new level of integration has been introduced which is known as ultra large scale integration (ULSI). In ULSI technique, more than one million active devices are integrated on a single chip. Pentium microprocessors use ULSI technology.

Que 1.7. Discuss the hierarchy of various semiconductors with Moore's law. Draw the Y-chart and explain the VLSI design process.

AKTU 2019-20, Marks 07

#### Answer

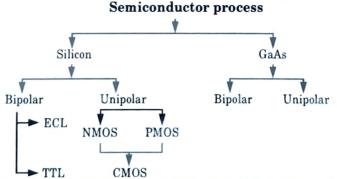

A. Hierarchy of various semiconductors with Moore's law : Hierarchy of various technology

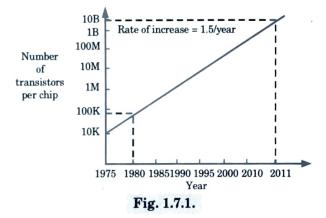

- 1. The IC was invented in February 1959 by Jack Kilby of Texas Instrument. The planar version of the IC was developed by Robert Noyce at Fairchild in July 1959. Since then the evolution of this technology has been extremely fast paced.

- 2. One way to gauge the process of the field is to look at the complexity of IC's as a function of time.

- 3. When we plot log of the component count as a function of time, we get a straight line, indicating that there has been an exponential growth in the complexity of chips over three decades.

#### VLSI Design

- 4. The component count has roughly doubled every 18 months, as was noted early by Gordon Moore. This regular doubling is known as Moore's law.

- 5. The main factor that has enabled this increase of complexity is the ability to shrink or scale devices.

- 6. Clearly, one can pack a larger number of components with greater functionality on an IC if they are smaller; also being advantageous in terms of faster IC's which consume less power.

- 7. Fig. 1.7.1 shows the level of integration versus time for memory chips.

- 8. It can be observed that in terms of transistor count, logic chips contain significantly fewer transistors in any given years mainly due to large consumption of chip area for complex interconnects.

- 9. Memory circuits are highly regular and thus more cells can be integrated with much less area for interconnects.

- 10. The demand for digital CMOS IC's will continue to be strong due to salient features such as low power, reliable performance, circuit techniques for high speed such as using dynamic circuits.

- 11. It is now projected that the minimum feature size in CMOS ICs can decrease up to 35 nm within a decade.

- 12. Bipolar and gallium arsenide (GaAs) circuits have been used for very high speed circuits, and this practice may continue. MMIC's, GaAs MESFET technology has been highly successful.

- 13. As long as the downward scaling of CMOS technology remains strong, other technologies are likely to remain the technology of tomorrow.

- B. Y-chart and VLSI design process : Refer Q. 1.1, Page 1-2F, Unit-1.

1-10 F (EC-Sem-7)

#### **Questions-Answers**

Long Answer Type and Medium Answer Type Questions

#### Que 1.8. What are the VLSI design styles ? Explain any one.

#### Answer

The VLSI design styles are :

- i. Gate array design

- ii. Standard-cells based design

- iii. Full custom design

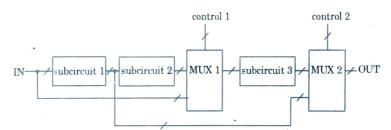

- iv. Field Programmable Gate Array (FPGA) :

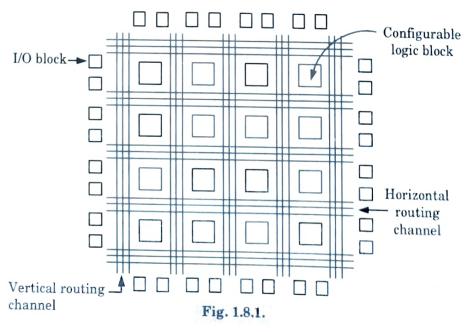

- 1. Fully fabricated FPGA chips containing thousands of logic gates or even more, with programmable interconnects, are available to users for their custom hardware programming to realize desired functionality.

- 2. This design style provides a means for fast prototyping and also for cost-effective chip design, especially for low-volume applications.

- 3. A typical FPGA chip consists of I/O buffers, an array of configurable logic blocks (CLBs), and programmable interconnect structures.

- 4. The programming of interconnects is implemented by programming of RAM cells whose output terminals are connected to the gates of MOS pass transistors. A general architecture of FPGA from XILINX is shown in Fig. 1.8.1.

#### VLSI Design

#### 1-11 F (EC-Sem-7)

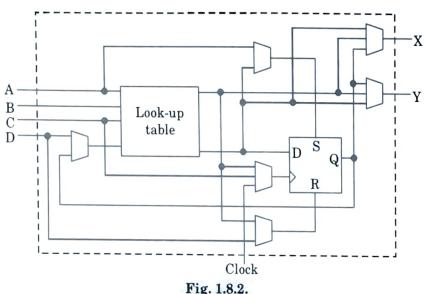

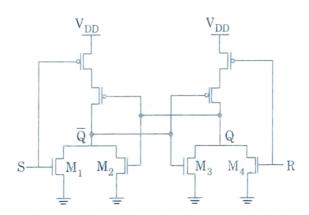

5. A simple CLB is shown in Fig. 1.8.2. It consists of four signal input terminals (A, B, C, D), a clock signal terminal, user-programmable multiplexers, an SR-latch, and a look-up table (LUT).

- 6. The LUT is a digital memory that stores the truth table of the boolean function. Thus, it can generate any function of upto four variables or any two functions of three variables.

- 7. The CLB is configured such that many different logic functions can be realized by programming its array.

#### Que 1.9. Write a short note on gate array design.

#### Answer

- 1. Gate array implementation requires a two-step manufacturing process. The first phase, which is based on generic (standard) masks, results in an array of uncommitted transistors on each GA chip.

- 2. These uncommitted chips can be stored for later customization, which is completed by defining the metal interconnects between the transistors of the array.

- 3. Since the patterning of metallic interconnects is done at the end of the chip fabrication, the turn-around time can be still short, a few days to a few weeks.

- 4. A corner of a gate array chip which contains bonding pads on its left and bottom edges, diodes for I/O protection, nMOS transistors and pMOS transistors for chip output driver circuits in the neighboring areas of bonding pads, arrays of nMOS transistors and pMOS transistors, underpass wire segments, and power and ground buses along with contact windows.

#### 1-12 F (EC-Sem-7)

- 5. Typical gate array platforms allow dedicated areas, called channels, for intercell routing between rows or columns of MOS transistors.

- 6. The availability of these routing channels simplifies the interconnections, even using one metal layer only.

- 7. The interconnection patterns that perform basic logic gates can be stored in a library, which can then be used to customize rows of uncommitted transistors according to the netlist.

- 8. In general, the GA chip utilization factor, as measured by the used chip area divided by the total chip area, is higher than that of the FPGA and so is the chip speed, since more customized design can be achieved with metal mask designs.

- 9. The current gate array chips can implement as many as of thousands of logic gates.

#### Que 1.10. Explain standard-cells based design.

#### Answer

- 1. The standard-cells based design is one of the most prevalent full custom design styles which require development of a full custom mask set.

- 2. The standard cell is also called the polycell.

- 3. In this design style, all of the commonly used logic cells are developed, characterized, and stored in a standard cell library.

- 4. A typical library may contain a few hundred cells including inverters, NAND gates, NOR gates, complex AOI, OAI gates, *D*-latches, and flip-flops.

- 5. The characterization of each cell is done for several different categories. It consists of :

- i. Delay time versus load capacitance

- ii. Circuit simulation model

- iii. Timing simulation model

- iv. Fault simulation model

- v. Cell data for place-and-route

- vi. Mask data.

- 6. To enable automated placement of the cells and routing of inter-cell connections, each cell layout is designed with a fixed height, so that a number of cells can be abutted side-by-side to form rows.

- 7. The power and ground rails typically run parallel to the upper and lower boundaries of the cell, thus, neighboring cells share a common power and ground bus.

- 8. The input and output pins are located on the upper and lower boundaries of the cell.

#### VLSI Design

#### Que 1.11. Discuss full custom design in brief.

#### Answer

- 1. In a full custom design, the entire mask design is done anew without use of any library. However, the development cost of such a design style is becoming prohibitively high.

- 2. Thus, the concept of design reuse is becoming popular in order to reduce design cycle time and development cost.

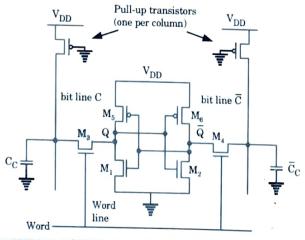

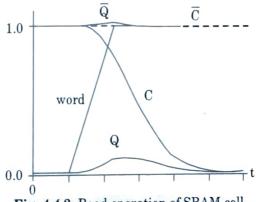

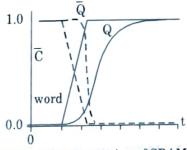

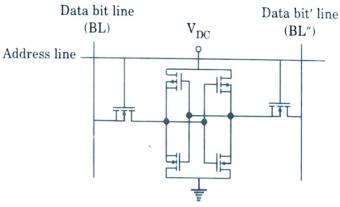

- 3. The most rigorous full custom design can be the design of a memory cell, be it static or dynamic. Since the same layout design is replicated, there would not be any alternative to high density memory chip design.

- 4. For logic chip design, a good compromise can be achieved by using a combination of different design styles on the same chip, such as standard cells, data-path cells and PLAs.

- 5. In real full-custom layout in which the geometry, orientation and placement of every transistor is done individually by the designer, design productivity is usually very low typically 10 to 20 transistors per day, per designer.

Packaging.

Que 1.12. Define the following method :

- i. PTH packages

- ii. SMT packages

OR

What are the types of common IC packages ? Explain.

#### Answer

- **A. PTH packages :** The package pins can be introduced in holes drilled in the PCB which is called pin-through-hole (PTH) method.

- **B. SMT packages :** The package pins can be directly soldered on the PCB which is called surface-mounted technology (SMT) method.

#### C. Some common IC package ( pes are :

#### i. Dual in-line packages (DIP) :

- 1. Dual in line packages (DIP) are characterized by their high interconnect inductances, which can lead to significant noise problems in high-frequency applications.

- 2. The maximum pin count of DIP is typically limited to 64.

- 3. DIP has the advantage of low cost but their dimensions can be prohibitive, especially for small, portable product.

#### ii. Pin grid array (PGA) packages :

- 1. This PTH package type offers a higher pin count and higher thermal conductivity compared to DIPs, especially when a passive or active heat sink is attached on the package.

- 2. The PGA packages require a large PCB area, and the package cost is higher than DIP, especially for ceramic PGAs.

#### iii. Chip carrier packages (CCP) :

- 1. This SMT package type is available in two variations, the leadless chip carrier and the leaded chip carrier.

- 2. The leadless chip carrier is designed to be mounted directly on the PCB, and it can support a high pin count.

- 3. The leaded chip carrier package solves this problem since the added leads can accommodate small dimension variations caused by the difference in the thermal coefficients.

#### iv. Quad flat packs (QFP) :

- 1. This SMT package type is similar to leaded chip carrier packages, except that the leads extend outward rather than being bent under the package body.

- 2. Ceramic and plastic QFPs with very high pin counts are becoming popular package types in recent years.

#### v. Multi-chip modules (MCM) :

- 1. This IC package option can be used for special applications requiring very high performance, where multiple chips are assembled on a common substrate contained in a single package.

- 2. Thus, a large number of critical interconnections between the chips can be made within the package.

CMOS Logic.

Questions-Answers Long Answer Type and Medium Answer Type Questions

## VLSI Design Bachelor Exam. Com

#### Que 1.13. Draw and explain the working of CMOS inverter with

#### its transfer characteristics.

AKTU 2018-19, Marks 10

#### Answer

#### **CMOS inverter :**

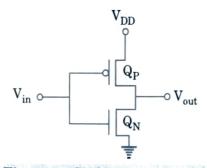

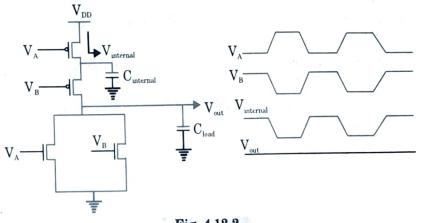

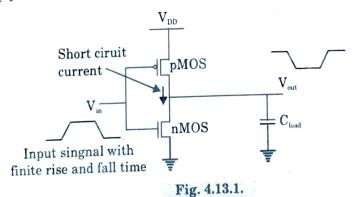

1. Fig. 1.13.1 shows the CMOS inverter. In the CMOS inverter, the PMOS and NMOS devices  $Q_P$  and  $Q_N$  are driven simultaneously by an input  $V_{in}$ .

Fig. 1.13.1 CMOS inverter circuit.

#### **Circuit operation :**

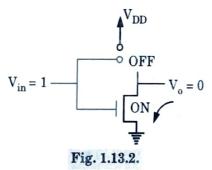

1. When input is high  $(= V_{DD}) Q_N$  is made to conduct, while  $Q_P$  is forced to cut-off. This causes the output becomes low  $(V_o = 0)$  as shown in Fig. 1.13.2.

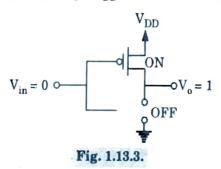

2. When input is low ( $\approx 0$  V)  $Q_N$  is OFF and  $Q_P$  becomes ON, therefore the output becomes logic high ( $V_q = V_{DD}$ ) as shown in Fig. 1.13.3.

3. Table 1.13.1 shows the operation of COMS inverter circuit.

#### Table 1.13.1.

| V <sub>in</sub> | Q <sub>P</sub> | Q <sub>N</sub> | Vo |

|-----------------|----------------|----------------|----|

| 0               | ON             | OFF            | 1  |

| 1               | OFF            | ON             | 0  |

#### Voltage transfer characteristics :

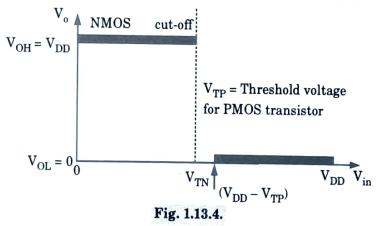

- 1. As shown in Fig. 1.13.4, the more positive output voltage corresponds to a logic 1 is  $V_{OH} = V_{DD}$ , and the more negative output voltage corresponds to a logic 0 is  $V_{OL} = 0$ .

- 2. When output is in the logic 0 state, the PMOS transistor is cut-off and when the output is in the logic 1 state, the NMOS transistor is cut-off.

### Que 1.14. Sketch a 2-input CMOS NAND gate and also discuss its working.

#### Answer

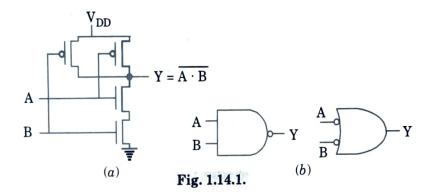

- 1. Fig. 1.14.1(a) shows a 2-input CMOS NAND gate. It consists of two series nMOS transistors between Y and GND and two parallel pMOS transistors between Y and  $V_{DD}$ .

- 2. If either input A or B is '0,' at least one of the nMOS transistors will be OFF, breaking the path from Y to GND. But at least one of the pMOS transistors will be ON, creating a path from Y to  $V_{DD}$ . Hence, the output Y will be '1'.

- 3. If both inputs are '1', both of the nMOS transistors will be ON and both of the pMOS transistors will be OFF. Hence, the output will be '0'.

- 4. The truth table is given below and the symbol is shown in Fig. 1.14.1(b).

VLSI Design

1-17 F (EC-Sem-7)

#### NAND gate truth table

| A | B | pull-down network | pull-up network | Y |

|---|---|-------------------|-----------------|---|

| 0 | 0 | OFF               | ON              | 1 |

| 0 | 1 | OFF               | ON              | 1 |

| 1 | 0 | OFF               | ON              | 1 |

| 1 | 1 | ON                | OFF             | 0 |

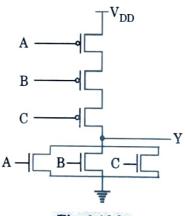

#### Que 1.15. Write a short note on combinational logic.

#### Answer

- 1. The inverter and NAND gates are examples of complementary CMOS logic gates, also called static CMOS gates.

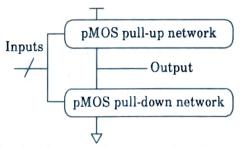

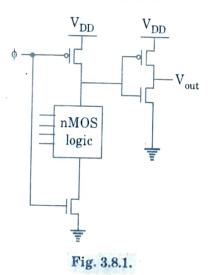

- 2. In general, a fully complementary CMOS gate has an nMOS pull-down network to connect the output to '0' (GND) and pMOS pull-up network to connect the output to '1'  $(V_{DD})$  as shown in Fig. 1.15.1. The networks are arranged such that one is ON and the other OFF for any input pattern.

- 3. The NAND gate used a series pull-down network and a parallel pull-up network.

Fig. 1.15.1. General logic gate using pull-up and pull-down network.

#### 1-18 F (EC-Sem-7)

Introduction

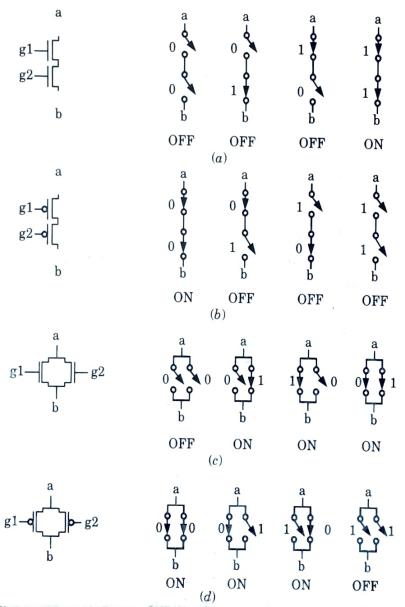

- 4. Two or more transistors in series are ON only if all of the series transistors are ON. Two or more transistors in parallel are ON if any of the parallel transistors are ON. This is shown Fig. 1.15.2 for nMOS and pMOS transistor pairs.

- 5. By using combinations of these constructions, CMOS combinational gates can be constructed.

Fig. 1.15.2. Connection and behaviour of series and parallel transistors.

6. The possible levels at the output are shown in Table 1.15.1. The '1' and '0' levels have been encountered with the inverter and NAND gates, where either the pull-up or pull-down is OFF and the other structure is ON.

#### VLSI Design

#### 1-19 F (EC-Sem-7)

- 7. When both pull-up and pull-down are OFF, the high-impedance or floating Z output state results. This is of importance in multiplexers, memory elements and bus drivers.

- 8. The crowbarred X level exists when both pull-up and pull-down are simultaneously turned ON.

- 9. This causes an indeterminate level and also static power to be dissipated. It is usually an unwanted condition in any CMOS digital circuit.

#### Table 1.15.1. Output states of CMOS logic gate

|               | pull-up OFF | pull-up ON     |

|---------------|-------------|----------------|

| pull-down OFF | Z           | 1              |

| pull-down ON  | 0           | crowbarred (X) |

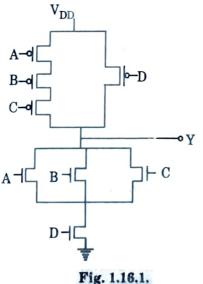

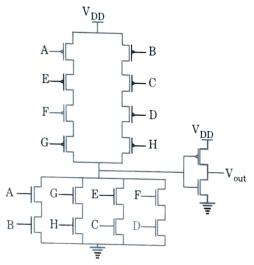

### Que 1.16. Implement the CMOS logic for the following Boolean

expression.

- i.  $Y = (A + B + C) \cdot D$ ii.  $Y = (A + B + C)(D + E) \cdot F$

- iii. 3 input NOR gate

AKTU 2017-18, Marks 10

Answer

$\mathbf{i.} \quad Y = (A + B + C) \cdot D$

#### 1-20 F (EC-Sem-7)

Introduction

**ii.**  $Y = (A + B + C) (D + E) \cdot F$

iii. 3 input NOR gate :

Fig. 1.16.3.

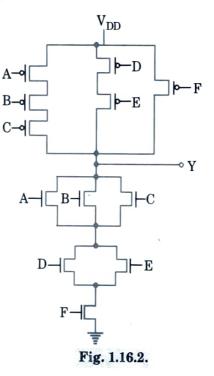

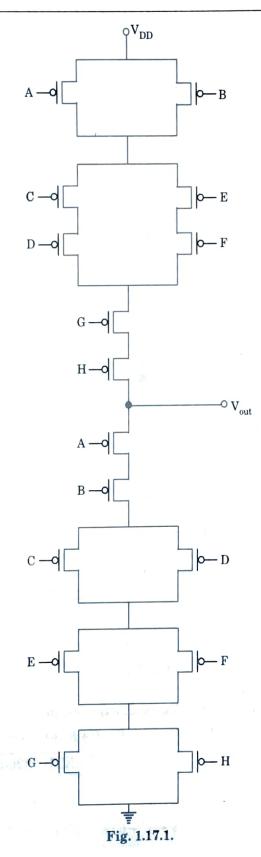

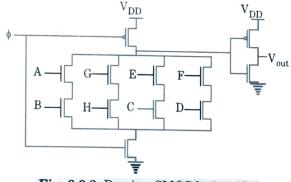

Que 1.17. Implement the Boolean expression

Y = AB + (C + D) (E + F) + (G + H).

AKTU 2020-21, Marks 07

Answer

Given,

Y = AB + (C + D) (E + F) + (G + H)

#### VLSI Design

1-21 F (EC-Sem-7)

#### 1-22 F (EC-Sem-7)

Introduction

#### PART-8

Propagation Delay Definitions.

#### **Questions-Answers**

Long Answer Type and Medium Answer Type Questions

#### Que 1.18. Explain propagation delay time.

#### Answer

- 1. The propagation delay time  $\tau_{PHL}$  and  $\tau_{PLH}$  determine the input-to-output signal delay during the high-to-low and low-to-high transitions of the output, respectively.

- 2. By definition,  $\tau_{PHL}$  is the time delay between the  $V_{50\%}$ -transition of the rising input voltage and the  $V_{50\%}$ -transition of the falling output voltage.

- 3. Similarly,  $\tau_{\rm PHL}$  is defined as the time delay between the  $V_{50\%}$ -transition of the falling input voltage and the  $V_{50\%}$ -transition of the rising output voltage.

PART-9

Sheet Resistance.

### Questions-Answers Long Answer Type and Medium Answer Type Questions

#### Que 1.19. Write a short note on sheet resistance.

#### Answer

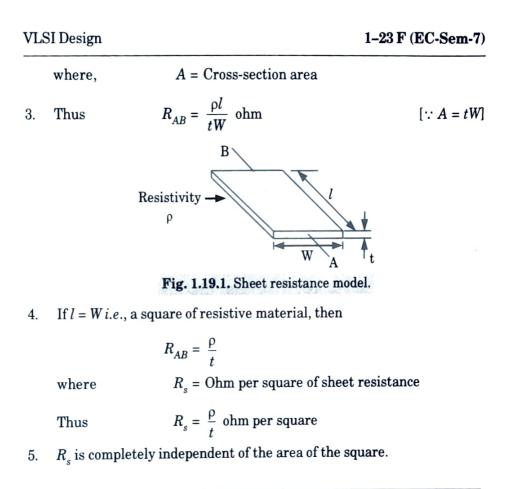

- 1. Consider a uniform slab of conducting material of resistivity  $\rho$ , of width W, thickness t, and length between faces l. The arrangement is shown in Fig. 1.19.1.

- 2. Consider the resistance  $R_{AB}$  between two opposite faces.

$$R_{AB} = \frac{\rho l}{A}$$

### Interconnect Parameters

### CONTENTS

| Part-1 | : | Resistance, Inductance <b>2–2F to 2–6F</b><br>and Capacitance |

|--------|---|---------------------------------------------------------------|

| Part-2 | : | Skin Effect and Its Influence 2-6F to 2-7F                    |

| Part-3 | : | Lumped RC Model 2-7F to 2-9F                                  |

| Part-4 | : | The Distributed RC Model 2-9F to 2-10F                        |

| Part-5 | : | Transient Response 2-10F to 2-12F                             |

| Part-6 | : | RC Delay Model 2-12F to 2-17F                                 |

| Part-7 | : | Linear Delay Model 2-17F to 2-21F                             |

| Part-8 | : | Logical Effort of 2-22F to 2-24F<br>Paths, Scaling            |

2-1 F (EC-Sem-7) BachelorExam.com

#### PART-1

Resistance, Inductance and Capacitance.

**Questions-Answers**

Long Answer Type and Medium Answer Type Questions

#### Que 2.1. How to compute the resistance of wire or interconnect?

#### Answer

1. The resistance of a uniform slab of conducting material can be expressed as

$$R = \frac{\rho}{t} \frac{l}{w} \qquad \dots (2.1.1)$$

where  $\rho$  is the resistivity. This expression can be rewritten as

$$R = R_s \frac{l}{w} \qquad \dots (2.1.2)$$

where,  $R_s = \frac{\rho}{t}$  is the sheet resistance and has units of  $\Omega$ /square.

- 2. To obtain the resistance of a conductor on a layer, multiply the sheet resistance by the ratio of length to width of the conductor.

- 3. The resistivity of thin metal films used in wires tends to be higher because of scattering off the surfaces and grain boundaries.

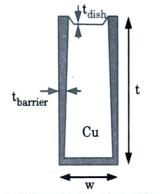

- 4. As shown in Fig. 2.1.1, copper must be surrounded by a lower-conductivity diffusion barrier that effectively reduces the wire cross-sectional area and hence raises the resistance. Moreover, the polishing step can cause dishing that thins the metal.

- 5. If the average barrier thickness is  $t_{\text{barrier}}$  and the height is reduced by  $t_{\text{dish}}$ , the resistance becomes,

$$R = \frac{\rho}{(t - t_{\text{dish}} - t_{\text{barrier}})} \frac{l}{(w - 2t_{\text{barrier}})} \qquad \dots (2.1.3)$$

- 6. The resistivity of polysilicon, diffusion, and wells is significantly influenced by the doping levels.

- 7. Polysilicon and diffusion typically have sheet resistances under 10  $\Omega$ /square when silicided and up to several hundred  $\Omega$ /square when unsilicided.

- 8. Wells have lower doping and thus even higher sheet resistance. Large resistors are often made from wells or unsilicided polysilicon.

### BachelorExam.com VLSI Design 2-3 F (EC-Sem-7)

- 9. Contacts and vias also have a resistance, which is dependent on the contacted material and size of the contact.

- 10. Multiple contacts should be used to form low-resistance connections, as shown in Fig. 2.1.2.

- 11. When current turns at a right angle or reverse, a square array of contacts is generally required, while fewer contacts can be used when the flow is in the same direction.

Fig. 2.1.2. Multiple bias for low-resistance connections.

Que 2.2. How to model the capacitance of wires ?

OR

Mention the advantages of interconnect modeling. Describe the interconnect modeling to calculate R and C.

AKTU 2020-21, Marks 07

OR

What are interconnecting models? Explain any two of them in brief.

AKTU 2017-18, Marks 10

Answer

- A. Interconnect models : The wires linking the transistors together are called interconnect. Interconnect models are :

- i. Resistor

- ii. Capacitor

- iii. Inductor.

BachelorExam.com 2-4 F (EC-Sem-7) Interconnect Parameters

**B.** Advantages of interconnect modeling: The interconnect modeling can be used efficiently during high-level design space exploration, interconnect-driven design planning, and synthesis- and timing-driven placement to ensure design convergence for deep sub-micrometer designs.

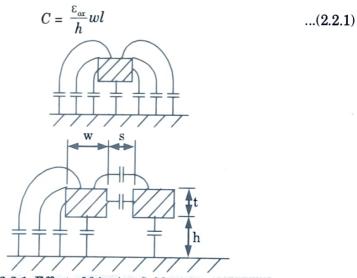

#### C. Capacitance model:

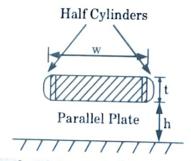

- 1. The wire capacitance has two major components: the parallel plate capacitance of the bottom of the wire to ground and the fringing capacitance arising from fringing fields along the edge of a conductor with finite thickness.

- 2. In addition, a wire adjacent to a second wire on the same layer can exhibit capacitance to that neighbour. These effects are illustrated in Fig. 2.2.1.

- 3. The parallel plate capacitance formula is

Fig. 2.2.1. Effect of fringing fields on capacitance.

4. The fringing capacitance is more complicated to compute. One intuitively appealing approximation treats a lone conductor above a ground plane as a rectangular middle section with two hemispherical end caps, as shown in Fig. 2.2.2.

Fig. 2.2.2. Yuan and trick capacitance model including fringing fields.

#### VLSI Design

$2-5 \mathbf{F} (\mathbf{EC} \cdot \mathbf{Sem} \cdot \mathbf{7})$

- The total capacitance is assumed to be the sum of a parallel plate capacitor 5. of width w - t/2 and a cylindrical capacitor of radius t/2.

- This results in an expression for the capacitance that is accurate within 6. 10 % for aspect ratios less than 2 and t = h.

$$C = \varepsilon_{\alpha x} l \left[ \frac{w - \frac{t}{2}}{h} + \frac{2\pi}{\ln\left(1 + \frac{2h}{t} + \sqrt{\frac{2h}{t}\left(\frac{2h}{t} + 2\right)}\right)} \right] \qquad \dots (2.2.2)$$

٦

An empirical formula that is computationally efficient and relatively 7. accurate is

$$C = \varepsilon_{ox} l \left[ \frac{w}{h} + 0.77 + 1.06 \left( \frac{w}{g} \right)^{0.25} + 1.06 \left( \frac{t}{h} \right)^{0.5} \right] \qquad \dots (2.2.3)$$

which is good to 6 % for aspect ratio less than 3.3.

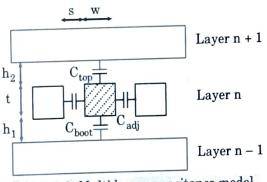

A cross-section of the model used for capacitance upper bound 8. calculations is shown in Fig. 2.2.3.

Fig. 2.2.3. Multi layer capacitance model.

The total capacitance of the conductor of interest is the sum of its 9. capacitance to the layer above, the layer below, and the two adjacent conductors.

$$C_{\text{total}} = C_{\text{top}} + C_{\text{boot}} + 2C_{\text{adj}}$$

=  $\varepsilon_o l \left[ 2k_{\text{vert}} \frac{w}{h} + 2k_{\text{horiz}} \frac{t}{s} \right] + C_{\text{fringe}}$  ...(2.2.4)

D. Resistance model: Refer Q. 2.1, Page 2–2F, Unit-2.

#### How to model the inductance of wires ? Que 2.3.

#### Answer

Inductance is difficult to extract and model, so engineers prefer to design in such a way that inductive effects are negligible. Nevertheless, 1. inductance needs to be considered in high-speed designs for wide wires such as clocks and power busses.

#### 2-6 F (EC-Sem-7)

**Interconnect Parameters**

- 2. Current flowing around a loop generates a magnetic field proportional to the area of the loop and the amount of current.

- 3. Changing the current requires supplying energy to change the magnetic field. This means that changing current induces a voltage proportional to the rate of change. The constant of proportionality is called the inductance.

$$V = L \frac{dI}{dt} \qquad \dots (2.3.1)$$

4. Inductance and capacitance also set the speed of light in a medium. Even if the resistance of a wire is zero leading to zero RC delay, the speed of light flight-time along a wire of length with inductance and capacitance per unit length of L and C is

$$t_{pd} = l\sqrt{LC} \qquad \dots (2.3.2)$$

5. If the current return paths are the same as the conducts on which electric field lines terminate, the signal velocity v is

$$v = \frac{1}{\sqrt{LC}} = \frac{1}{\sqrt{\varepsilon_{ax}\mu_0}} = \frac{c}{\sqrt{3.9}}$$

...(2.3.3)

where,  $\mu_0$  is the magnetic permeability of free space  $(4\pi \times 10^{-7} \text{H/m})$  and c is the speed of light in free space  $(3 \times 10^8 \text{ m/s})$ .

- 6. Changing magnetic fields in turn produce currents in other loops. Hence, signals on one wire can inductively couple onto another, this is called inductive crosstalk.

- 7. The inductance of a conductor of length l and width w located a height h above a ground plane is approximately

$$L = l \frac{\mu_0}{2\pi} \ln \left( \frac{8h}{w} + \frac{w}{4h} \right) \qquad ...(2.3.4)$$

assuming w < h and thickness is negligible.

8. Inductance depends on the entire loop and therefore cannot be simply decomposed into sections as with capacitance. It is therefore impractical to extract the inductance from a chip layout.

### PART-2

Skin Effect and Its Influence.

Que 2.4. Write a short note on skin effect.

#### VLSI Design

#### Answer

- 1. Current flows along the path of lowest impedance  $Z = R + j\omega L$ . At high frequency,  $\omega$ , impedance becomes dominated by inductance.

- 2. The inductance is minimized if the current flows only near the surface of the conductor closer to the return path.

- 3. This skin effect can reduce the effective cross-sectional area of thick conductors and raise the effective resistance at high frequency.

- 4. The skin depth for a conductor is

$$\delta = \sqrt{\frac{2\rho}{\omega\mu}} \qquad \dots (2.4.1)$$

where,  $\mu$  is the magnetic permeability of the dielectric.

- 5. The frequency of importance is the highest frequency with significant power in the Fourier transform of the signal. This is not the chip operating frequency, but rather is associated with the faster edges.

- 6. A sine wave with the same 20-80 % rise/fall time as the signal has a period of 8.65  $t_{rf}$ . Therefore, the frequency associated with the edge can be approximated as

$$\omega = \frac{2\pi}{8.65t_{rf}} \qquad ...(2.4.2)$$

where,  $t_{rf}$  is the average 20-80 % rise/fall time.

Que 2.5. What do you mean by lumped *RC* model ? Also explain RC network.

OR

Explain the Elmore delay model with suitable *RC* networks. Mention its merits. AKTU 2020-21, Marks 07

OR

Explain the Elmore delay model with suitable diagram.

AKTU 2018-19, Marks 10

#### 2-8 F (EC-Sem-7)

#### Answer

- A. Lumped RC model: A first approach lumps the total wire resistance of each wire segment into one single R and similarly combines the capacitance into a single capacitor C. This simple model, called the lumped RC model.

- B. Register capacitor network (Elmore delay model) :

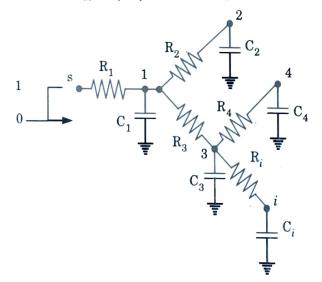

- 1. Consider the resistor-capacitor network of Fig. 2.5.1.

- 2. The result of this circuit topology is that there exists a unique resistive path between the source node s and any node i of the network. The total resistance along this path is called the path resistance  $R_{ii}$ .

- 3. For example, the path resistance between the source node s and node 4 is,

$$R_{44} = R_1 + R_3 + R_4$$

4. The shared path resistance  $R_{ik}$ , which represents the resistance shared among the paths from the root node *s* to nodes *k* and *i*:

$R_{ik} = R_i (R_i \text{ [path(s i)... path(s k)]})$

Fig. 2.5.1. Tree structure RC network.

- 5. Assume now that each of the N nodes of the network is initially discharged to GND, and that a step input is applied at node s at time t = 0.

- 6. The Elmore delay at node *i* is then given by the following expression :

$$T_{Di} = \sum_{k=1}^{N} C_k R_{tk}$$

#### C. Merits of Elmore delay model :

i. Simple closed-form expression.

#### VLSI Design

- ii. Useful for interconnect optimization.

- iii. Upper bound of 50 % delay.

- iv. High fidelity.

#### Que 2.6. Draw and explain the working of Lumped *RC*-model for

#### interconnects.

AKTU 2018-19, Marks 10

#### Answer

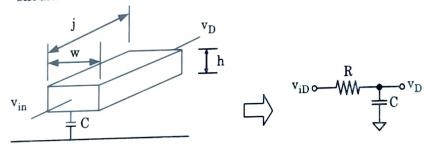

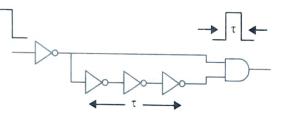

1. When the physical dimension, in particular, the length, of a wire channel is much smaller as compared with the wavelength of the signal passing through the channel, the channel can be treated as a lumped element with its characteristics depicted by a low-pass RC network, as shown in Fig. 2.6.1, with

$C \approx C_a(wl) + 2C_f l$

where  $C_a$  is the area capacitance per unit area and

$C_f$  is the fringe capacitance per unit length of the wire channel.

- 2. A more rigorous criterion on whether lumped models should be used to characterize the behavior of channels is determined by comparing the round-trip time that the signal travels along the channels, denoted by  $2\tau$  where  $\tau$  is the time for the signal to travel from one end of the channel to the other, and the rise time of the signal  $t_r$ .

- 3. If  $2\tau < t_r$ , lumped models should be used. Otherwise, distributed models should be used.

Fig. 2.6.1. Lumped RC model of wire channels.

#### 2-10 F (EC-Sem-7)

#### Que 2.7. Explain distributed RC model.

#### Answer

- 1. A wire is a distributed circuit with a resistance and capacitance per unit length.

- 2. Its behavior can be approximated with a number of lumped elements.

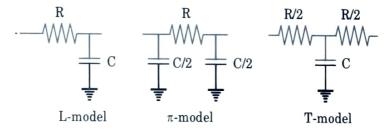

- 3. Three standard approximations are the *L*-model,  $\pi$ -model, and *T*-model, so named because of their shapes.

- 4. Fig. 2.7.1 shows how a distributed RC circuit is equivalent to N distributed RC segments of proportionally smaller resistance and capacitance, and how these segments can be modeled with lumped elements.

Fig. 2.7.1. Lumped approximation to distributed RC circuit.

- 5. As the number of segments approaches infinity, the lumped approximation will converge with true distributed circuit.

- 6. The *L*-model is a poor choice because a large number of segments are required for accurate results.

- 7. The  $\pi$ -model is much better, three segments are sufficient to give results accurate to 3 %.

- 8. The *T*-model is comparable to the  $\pi$ -model, but produces a circuit with one more node that is slower to solve by hand or with a circuit simulator.

- 9. Therefore, it is common practice to model long wires with a 3-5 segment  $\pi$ -model for simulation.

PART-5

Transient Response.

#### VLSI Design

### Que 2.8. Compute the step response (or transient response) of an inverter.

#### Answer

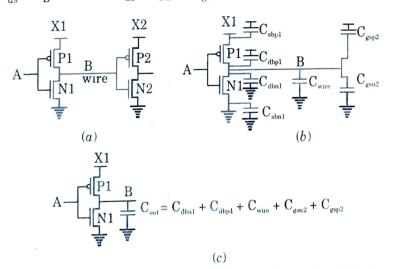

- 1. Fig. 2.8.1(*a*) shows an inverter  $X_1$  driving another inverter  $X_2$  at the end of a wire.

- 2. Suppose a voltage step from 0 to  $V_{DD}$  is applied to node A and to compute the propagation delay,  $t_{pd}$ , through  $X_1$ , *i.e.*, the delay from the input step until node B crosses  $V_{DD}/2$ .

- 3. These capacitances are shown in Fig. 2.8.1(b). Fig. 2.8.1(c) shows the equivalent circuit diagram in which all the capacitances are lumped into a single  $C_{out}$ .

- 4. Before the voltage step is applied, A = 0.  $N_1$  is OFF,  $P_1$  is ON, and  $B = V_{DD}$ .

- 5. After the step, A = 1.  $N_1$  turns ON and  $P_1$  turns OFF and B drops toward 0.

- 6. The rate of change of the voltage  $V_B$  at node B depends on the output capacitance and on the current through  $N_1$ :

$$C_{\text{out}} \frac{dV_B}{dt} = I_{dsn1} \qquad \dots (2.8.1)$$

7. Suppose the transistors obey the long-channel models. The current depends on whether  $N_1$  is in the linear or saturation region. The gate is at  $V_{DD}$ , the source is at 0, and the drain is at  $V_B$ . Thus,  $V_{gs} = V_{DD}$  and  $V_{ds} = V_B$ . Initially,  $V_{ds} = V_{DD} > (V_{gs} - V_t)$ , so  $N_1$  is in saturation.

Fig. 2.8.1. Capacitances for inverter delay calculations

8. As  $V_B$  falls below  $V_{DD} - V_t$ ,  $N_1$  enters the linear region. The differential equation governing  $V_B$  is given by,

#### 2-12 F (EC-Sem-7)

Interconnect Parameters

$$\frac{dV_B}{dt} = \frac{\beta}{C_{out}} \begin{cases} \frac{(V_{DD} - V_t)^2}{2} ; & V_B > V_{DD} - V_t \\ (V_{DD} - V_t - \frac{V_B}{2})V_B ; & V_B < V_{DD} - V_t \end{cases} \dots (2.8.2)$$

- 9. During saturation, the current is constant and  $V_B$  drops linearly until it reaches  $V_{DD} - V_t$ . Thereafter, the differential equation becomes non-linear. The response can be computed numerically.

- 10. Assuming  $V_{tn} + |V_{tp}| < V_{DD}$ , the ramp response includes three phases, as shown in Table 2.8.1. Thus, we can write the differential equations for  $V_B$  in each phase :

Phase 1:

$$V_{B} = V_{DD}$$

$$\frac{dV_{B}}{dt} = \frac{I_{dsp1} - I_{dsn1}}{C_{out}} \qquad \dots (2.8.3)$$

$$\frac{dV_{B}}{dt} = \frac{I_{dsn1}}{C_{out}}$$

Phase 3:

Phase 2:

$C_{out}$ Table 2.8.1. Phases of inverter ramp response :

dt

| Phase | V <sub>A</sub>                             | N <sub>1</sub> | <i>P</i> <sub>1</sub> | V <sub>B</sub>   |

|-------|--------------------------------------------|----------------|-----------------------|------------------|

| 1     | $0 < V_A < V_{tn}$                         | OFF            | ON                    | $V_{DD}$         |

| 2     | $V_{tn} < V_A < V_{DD} - \mid V_{tp} \mid$ | ON             | ON                    | Intermediate     |

| 3     | $V_{DD} -  V_{tp}  < V_A < V_{DD}$         | ON             | OFF                   | Falling toward 0 |

Discuss briefly about effective resistance. Also explain Que 2.9. gate and diffusion capacitance of RC delay model. OR

Explain RC delay model for interconnects.

AKTU 2020-21, Marks 07

OR

VLSI Design

#### Explain the concept of RC delay model. AKTU 2019-20, Marks 3.5

#### Answer

*RC* delay models approximate the non-linear transistor I-V and C-V characteristics with an average resistance and capacitance over the switching range of the gate.

#### A. Effective resistance :

- 1. The RC delay model treats a transistor as a switch in series with a resistor. The effective resistance is the ratio of  $V_{ds}$  to  $I_{ds}$  averaged across the switching interval of interest.

- $\cdot$  2. A unit nMOS transistor is defined to have effective resistance R.

- 3. An nMOS transistor of K times unit width has resistance R/K because it delivers K times as much current.

- 4. A unit pMOS transistor has greater resistance, generally in the range of 2R-3R, because of its lower mobility.

- 5. According to the long-channel model, current decreases linearly with channel length and hence resistance is proportional to *L*.

- 6. Moreover, the resistance of two transistors in series is the sum of the resistances of each transistor.

- 7. However, if a transistor is fully velocity-saturated, current and resistance become independent of channel length.

- 8. The resistance of transistors in series is somewhat lower than the sum of the resistances, because series transistors have smaller  $V_{ds}$  and are less velocity-saturated.

- 9. The effect is more pronounced for nMOS transistors than pMOS because of the higher mobility and greater degree of velocity saturation.

#### B. Gate and diffusion capacitance :

- 1. Each transistor has gate and diffusion capacitance.

- 2. A transistor of k times unit width has capacitance kC.

- 3. Diffusion capacitance depends on the size of the source/drain region. Wider transistors have proportionally greater diffusion capacitance.

- 4. Increasing channel length increases gate capacitance proportionally but does not affect diffusion capacitance.

Que 2.10. Draw and explain equivalent *RC* circuit models for nMOS and pMOS transistors. Also draw the equivalent circuit for an inverter.

### 2-14 F (EC-Sem-7)

#### Answer

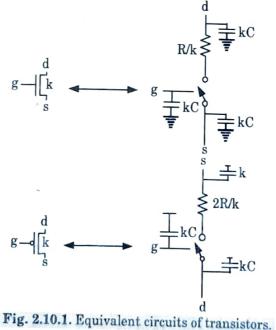

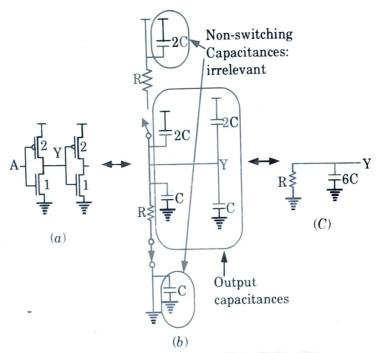

- Fig. 2.10.1 shows equivalent RC circuit models for nMOS and pMOS 1. transistors of width k with contacted diffusion on both source and drain

- 2. The pMOS transistor has approximately twice the resistance of the nMOS transistor because holes have lower mobility than electrons.

- The pMOS capacitors are shown with  $V_{DD}$  as their second terminal 3. because the n-well is usually tied high. Fig. 2.10.2 shows the equivalent circuit for a fanout-of-1 inverter with negligible wire capacitance.

- The unit inverters of Fig. 2.10.2(a) are composed from an nMOS 4. transistor of unit size and a pMOS transistor of twice unit width to achieve equal rise and fall resistance.

- Fig. 2.10.2(b) gives an equivalent circuit, showing the first inverter 5. driving the second inverter's gate.

- If the input A rises, the nMOS transistor will be ON and the pMOS 6. OFF. Fig. 2.10.2(c) illustrates this case with the switches removed.

- The capacitors shorted between two constant supplies are also removed 7. because they are not charged or discharged. The total capacitance on the output Y is 6C.

#### VLSI Design

Fig. 2.10.2. Equivalent circuit for an inverter

Que 2.11. Estimate  $t_{pd}$  (or step response) for first-order and second-order RC system.

#### Answer

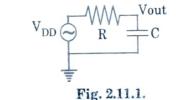

1. Consider applying the *RC* model to estimate the step response of the first-order system shown in Fig. 2.11.1.

This system is a good model of an inverter sized for equal rise and fall delays.

2. The system has a transfer function

$$H(S) = \frac{1}{1 + sRC} \qquad \dots (2.11.1)$$

and a step response

$$V_{\text{out}}(t) = V_{DD} e^{t/\tau}$$

...(2.11.2)

$\tau = RC$

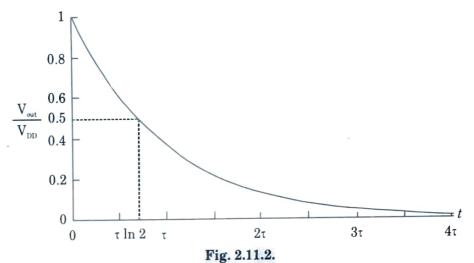

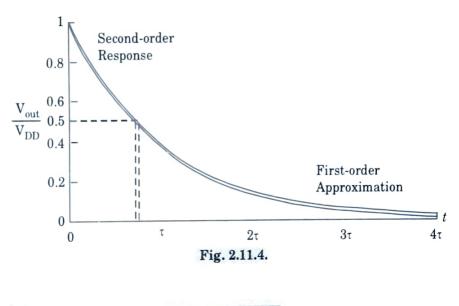

where,  $\tau = RC$ 3. The propagation delay is the time at which  $V_{out}$  reaches  $V_{DD}/2$ , as shown in Fig. 2.11.2.

$$t_{\rm nd} = RC \ln 2$$

...(2.11.3)

Interconnect Parameters

4. Here we define a new effective resistance  $R' = R \ln 2$ . Now the propagation delay is simply R-C. For the sake of convenience,

$$t_{nd} = RC$$

...(2.11.4)

where, the effective resistance R is chosen to give the correct delay.

- 6. Fig. 2.11.3 shows a second-order system.  $R_1$  and  $R_2$  might model the two series nMOS transistors in a NAND gate or an inverter driving a long wire with non-negligible resistance.

- 6. The transfer function is

$$H(s) = \frac{1}{1 + s[R_1C_1 + (R_1 + R_2)C_2] + s^2R_1C_1R_2C_2} \qquad \dots (2.11.5)$$

$$V_{DD} \underbrace{\bigvee_{DD} \underbrace{\bigvee_{DD} \bigvee_{T} & C_1}_{T} & C_2}_{T}$$

Fig. 2.11.3.

7. The function has two real poles and the step response is

$$V_{\text{out}}(t) = V_{DD} \frac{\tau_1 e^{t/\tau_1} \cdot \tau_2 e^{t/\tau_2}}{\tau_1 \cdot \tau_2} \qquad \dots (2.11.6)$$

with

$$\begin{aligned} \tau_{1,2} &= \frac{R_1 C_1 + (R_1 + R_2) C_2}{2} \left( 1 \pm \sqrt{\frac{4R^* C^*}{[1 + (1 + R^*)C^*]^2}} \right) \quad \dots (2.11.7) \\ R^* &= \frac{R_2}{R_1}; C^* = \frac{C_2}{C_1} \end{aligned}$$

8. Eq. (2.11.7) is so complicated that it defeats the purpose of simplifying a CMOS circuit into an equivalent RC network. However, it can be further approximated as a first-order system with a single time constant :

VLSI Design

2-17 F (EC-Sem-7)

$$\tau = \tau_1 + \tau_2 = R_1 C_1 + (R_1 + R_2) C_2 \qquad \dots (2.11.8)$$

- 9. This approximation works best when one time constant is significantly bigger than the other. For example, if  $R_1 = R_2 = R$  and  $C_1 = C_2$  then  $\tau_1 = 2.6 RC$ ,  $\tau_2 = 0.4 RC$ ,  $\tau = 3 RC$  and the second-order response and its first-order approximation are shown in Fig. 2.11.4.

- 10. The error in estimated propagation delay from the first-order approximation is less than 7 %.

Que 2.12. Explain linear delay model.

OR Explain the delay estimation with different optimization techniques. AKTU 2018-19, Marks 10

#### 2-18 F (EC-Sem-7)

#### **Interconnect Parameters**

#### Answer

Delay estimation with different optimization techniques are :

- i. Elmore delay : Refer Q. 2.5, Page 2–7F, Unit-2.

- ii. Linear delay :

- 1. The *RC* delay model showed that delay is a linear function of the fanout of a gate. Based on this observation, designers further simplify delay analysis by characterizing a gate by the slope and *y*-intercept of this function.

- 2. In general, the normalized delay of a gate can be expressed in units of  $\tau$  as

$$d = f + p$$

...(2.12.1)

where p is the parasitic delay inherent to the gate when no load is attached and f is the effort delay or stage effort that depends on the complexity and fanout of the gate :

$$f = gh$$

...(2.12.2)

3. The complexity is represented by the logical effort, g. An inverter is defined to have a logical effort of 1. More complex gates have greater logical efforts, indicating that they take longer to drive a given fanout.

#### VLSI Design

#### 2-19 F (EC-Sem-7)

4. A gate driving h identical copies of itself is said to have a fanout or electrical effort of h. If the load does not contain identical copies of the gate, the electrical effort can be computed as

$$h = \frac{C_{\text{out}}}{C_{\text{in}}}$$

...(2.12.3)

where,  $C_{\rm out}$  is the capacitance of the external load being driven and  $C_{\rm in}$  is the input capacitance of the gate.

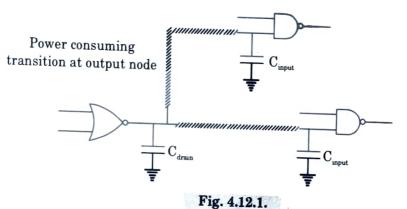

- 5. Fig. 2.12.1 plots normalized delay v/s electrical for an idealized inverter and 3-input NAND gate.

- 6. The y-intercepts indicate the parasitic delay, *i.e.*, the delay when the gate drives no load.

- 7. The slope of the lines is the logical effort.

- 8. The inverter has a slope of 1 by definition. The NAND has a slope of 5/3.

### Que 2.13. Analyze the linear delay model with its different

#### limitations.

AKTU 2018-19, Marks 10

Answer

- A. Linear delay model : Refer Q. 2.12, Page 2–17F, Unit-2.

- **B.** Limitations :

- a. Input and output slope :

- 1. The largest source of error in the linear delay model is the input slope effect.

- 2. As the rise time of the input increases, the delay also increases because the active transistor is not turned fully ON at once.

### b. Input arrival times :

- 1. Another source of error in the linear delay model is the assumption that one input of a multiple input gate switches while the others are completely stable.

- 2. When two inputs to a series stack turn ON simultaneously, the delay will be slightly longer than predicted because both transistors are only partially ON during the initial part of the transition.

- 3. When two inputs to a parallel stack turn ON simultaneously, the delay will be shorter than predicted because both transistors deliver current to the output.

#### 2-20 F (EC-Sem-7)

**Interconnect Parameters**

### Que 2.14. How to estimate the logical effort and parasitic delay?

OR

- Write short notes on :

- i. Logical effort

- ii. Parasitic delay.

AKTU 2018-19, Marks 10

OR

Define the term logical effort and electrical effort. Explain linear RC delay model. Mention the limitation of this model.

AKTU 2020-21, Marks 07

#### Answer

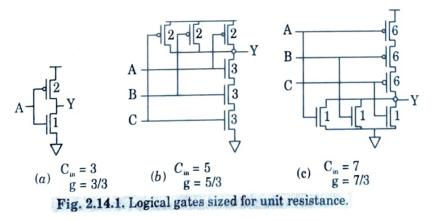

#### A. Logical effort :

- 1. Logical effort of a gate is defined as the ratio of the input capacitance of the gate to the input capacitance of an inverter that can deliver the same output current.

- 2. Logical effort indicates how much worse a gate is at producing output current as compared to an inverter, given that each input of the gate may only present as much input capacitance as the inverter.

- 3. Fig. 2.14.1 shows inverter, 3-input NAND, and 3-input NOR gates with transistors widths chosen to achieve unit resistance assuming pMOS transistors have twice the resistance of nMOS transistors.

- 4. The inverter presents three units of input capacitance. The NAND presents five units of capacitance on each input, so the logical effort is 5/3.

- 5. Similarly, the NOR presents seven units of capacitance, so the logical effort is 7/3. This matches our expectation that NANDs are better than NORs because NORs have slow pMOS transistors in series.

#### VLSI Design

#### 2-21 F (EC-Sem-7)

### Table 2.14.1 the logical effort of common gates

| Gate type             | Number of inputs |     |        |           |            |  |  |  |

|-----------------------|------------------|-----|--------|-----------|------------|--|--|--|

|                       | 1                | 2   | 3      | 4         | n          |  |  |  |

| Inverter              | 1                |     |        |           |            |  |  |  |

| NAND                  |                  | 4/3 | 5/3    | 6/3       | (n + 2)/3  |  |  |  |

| NOR                   |                  | 5/3 | 7/3    | 9/3       | (2n + 1)/3 |  |  |  |

| Tristate, Multiplexer | 2                | 2   | 2      | 2         | 2          |  |  |  |

| XOR, XNOR             |                  | 4,4 | 6,12,6 | 8,16,16,8 |            |  |  |  |

#### B. Parasitic delay :

- 1. The parasitic delay of a gate is the delay of the gate when it drives zero load. It can be estimated with *RC* delay models.

- 2. A crude method good for hand calculations is to count only diffusion capacitance on the output node.

- 3. For example, consider the gates in Fig. 2.14.1; assuming each transistor on the output node has its own drain diffusion contact.

- 4. Transistor widths were chosen to give a resistance of *R* in each gate.

- 5. The inverter has three units of diffusion capacitance on the output, so the parasitic delay is  $3RC = \tau$ . In other words, the normalized parasitic delay is 1.

- 6. In general, we will call the normalized parasitic delay  $p_{inv}.p_{inv}$  is the ratio of diffusion capacitance to gate capacitance in a particular process. **Table 2.14.2 the parasitic delay of common gates**

| Gate type             | Number of inputs |   |   |   |    |  |  |  |

|-----------------------|------------------|---|---|---|----|--|--|--|

| Read and a start      | 1                | 2 | 3 | 4 | n  |  |  |  |

| Inverter              | 1                |   |   |   |    |  |  |  |

| NAND                  |                  | 2 | 3 | 4 | n  |  |  |  |

| NOR                   |                  | 2 | 3 | 4 | n  |  |  |  |

| Tristate, Multiplexer | 2                | 4 | 6 | 8 | 2n |  |  |  |

- 7. The parasitic delay also depends on the ratio of diffusion capacitance to gate capacitance.

- **C.** Electrical effort : The effort delay of 4(b'/k)C = 4bC depends on the ratio (b) of external load capacitance to input capacitance and thus charges with transistor widths. The factor 4 is by the complexity of the gate. The capacitance ratio is called the electrical effort.

2-22 F (EC-Sem-7)

**Interconnect Parameters**

### PART-8

Logical Effort of Paths, Scaling.

**Questions-Answers**

Long Answer Type and Medium Answer Type Questions

Que 2.15. What do you understand by logical effort of paths? Also give the limitations of logical effort.

OR What are the limitations of logical effort ?

AKTU 2019-20, Marks 3.5

#### Answer

#### A. Logical effort of paths :

- 1. Designers often need to choose the fastest circuit topology and gate sizes for a particular logic function and to estimate the delay of the design.

- 2. Logical effort provides a simple method "on the back of an envelope" to choose the best topology and number of stages of logic for a function.

- 3. Based on the linear delay model, it allows the designer to quickly estimate the best number of stages for a path, the minimum possible delay for the given topology, and the gate sizes that achieve this delay.

#### B. Limitations of logical effort :

- 1. Logical effort does not account for interconnect. Logical effort is most applicable to high-speed circuits with regular layouts where routing delay does not dominate. Such structures include adders, multipliers, memories, and other datapaths and arrays.

- 2. Logical effort explains how to design a critical path for maximum speed, but not how to design an entire circuit for minimum area or power given a fixed speed constraint.

- 3. Paths with non-uniform branching or reconvergent fanout are difficult to analyze by hand.

- 4. The linear delay model fails to capture the effect of input slope. Fortunately, edge rates tend to be about equal in well-designed circuits with equal effort delay per stage.

#### VLSI Design

### Que 2.16. Why transistor scaling is of great importance in VLSI ? Write down comparison between constant-field scaling and

constant-voltage scaling.

AKTU 2017-18, Marks 10

AKTU 2019-20, Marks 07

#### Answer

- 1. The design of high-density chips in MOS VLSI technology requires that the packing density of MOSFETs used in the circuits is as high as possible and, consequently, that the sizes of the transistors are as small as possible. The reduction of the size, *i.e.*, the dimensions of MOSFETs, is commonly referred to as scaling.

- 2. Scaling of MOS transistors is concerned with systematic reduction of overall dimensions of the devices as allowed by the available technology, while preserving the geometric ratios found in the larger devices.

- 3. The proportional scaling of all devices in a circuit would certainly result in a reduction of the total silicon area occupied by the circuit, thereby increasing the overall functional density of the chip.

- There are two basic types of size-reduction strategies :

#### i. Constant-field scaling :

- 1. This scaling option attempts to preserve the magnitude of internal electric fields in the MOSFET, while the dimensions are scaled down by a factor of *S*. It is also known as full scaling.

- 2. To achieve this goal, all potentials must be scaled down proportionally, by the same scaling factor.

- 3. The full scaling reduces both the drain current and the drain-to-source voltage by a factor of S; hence, the power dissipation of the transistor will be reduced by the factor  $S^2$ .

$$P' = I'_D \cdot V'_{DS} = \frac{1}{S^2} I_D \cdot V_{DS} = \frac{P}{S^2} \qquad \dots (2.16.1)$$

The significant reduction of the power dissipation is one of the most attractive features of full scaling.

4. The proportional reduction of all dimensions on chip will lead to a reduction of various parasitic capacitances and resistances as well, contributing to the overall performance improvement.

### ii. Constant-voltage scaling :

1. In particular, the peripheral and interface circuitry may require certain voltage levels for all input and output voltages, which in turn would necessitate multiple power supply voltages and complicated level-shifter

#### 2-24 F (EC-Sem-7)

Interconnect Parameters

arrangements. Here, constant-voltages scaling is usually preferred over full scaling.

- 2. In constant-voltage scaling, all dimensions of the MOSFET are reduced by a factor of S, as in full scaling. The power supply voltage and the terminal voltages, on the other hand, remain unchanged.

- 3. The drain current is increased by a factor of S while the drain-to-source voltage remains unchanged, the power dissipation of the MOSFET increases by a factor of S.

$$P' = I'_D \cdot V'_{DS} = (S \cdot I_D) \cdot V_{DS} = S \cdot P$$

4. Constant-voltage scaling increases the drain current density and the power density by a factor of  $S^3$ . The large increase in current and power densities may eventually cause serious reliability problems for the scaled transistor, such as electromigration, hot-carrier degradation, oxide breakdown, and electrical over-stress.

### **Dynamic CMOS Design**

### CONTENTS

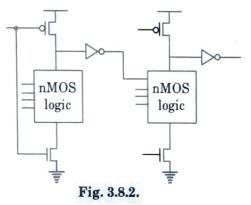

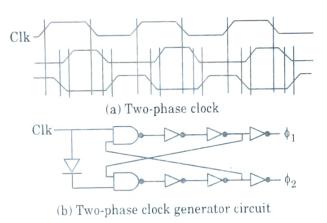

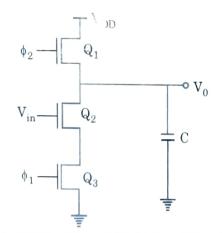

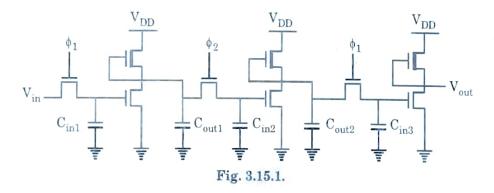

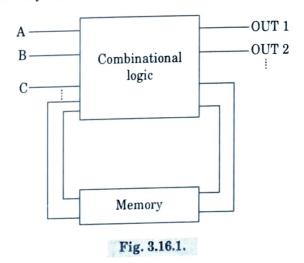

| Part-1 | : | Dynamic CMOS Design : <b>3-2F to 3-7F</b><br>Steady-State of<br>Dynamic Gate Circuits                        |

|--------|---|--------------------------------------------------------------------------------------------------------------|

| Part-2 | : | Noise Consideration in <b>3-7F to 3-10F</b><br>Dynamic Design, Charge<br>Sharing, Cascading<br>Dynamic Gates |

| Part-3 | : | Domino Logic 3-11F to 3-13F                                                                                  |

| Part-4 | : | NP-CMOS Logic 3-14F to 3-16F                                                                                 |

| Part-5 | : | Problems in Single-Phase <b>3-16F to 3-17F</b><br>Clocking                                                   |

| Part-6 | : | Two-Phase Non-overlapping <b>3-17F to 3-20F</b><br>Clocking                                                  |

| Part-7 | : | Sequential CMOS Logic 3-20F to 3-24F<br>Circuits, Layout Design                                              |

3-2 F (EC-Sem-7)

PART-1

Dynamic CMOS Design : Steady-State of Dynamic Gate Circuits.

#### **Questions-Answers**

Long Answer Type and Medium Answer Type Questions

Que 3.1. Explain the dynamic CMOS design.

### Answer

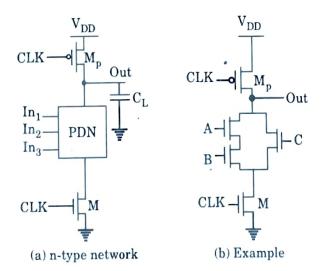

#### A. Dynamic CMOS design :

- 1. Dynamic circuit, which relies on temporary storage of signal values on the capacitance of high impedance circuit nodes.

- 2. In this, an alternate logic style called dynamic logic is presented that obtains a similar result, while avoiding static power consumption.

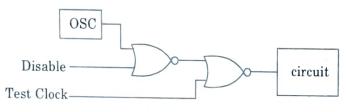

- 3. With the addition of a clock input, it uses a sequence of precharge and conditional evaluation phases.

#### B. Construction and working :

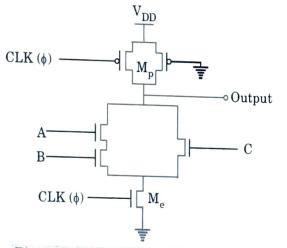

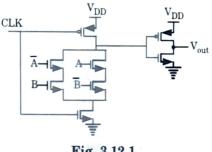

1. The basic construction of an (*n*-type) dynamic logic gate is shown in Fig. 3.1.1. The PDN (pull-down network) is constructed exactly as in complementary CMOS.

Fig. 3.1.1. Basic concepts of dynamic gate.

### VLSI Design

### 3-3 F (EC-Sem-7)

2. The operation of this circuit is divided into two major phases :

#### a. Precharge:

- i. When CLK = 0, the output node, Out is precharged to  $V_{DD}$  by the pMOS transistor  $M_p$ . During that time, the evaluate nMOS transistor  $M_e$  is OFF, so that the pull-down path is disabled.

- ii. The evaluation FET eliminates any static power that would be consumed during the precharge period (this is, static current would flow between the supplies if both the pull down and the precharge device were turned ON simultaneously).

#### b. Evaluation :

- i. For CLK = 1, the precharge transistor  $M_p$  is OFF, and the evaluation transistor  $M_e$  is turned ON.

- ii. The output is conditionally discharged based on the input values and the pull-down topology.

- iii. If the inputs are such that the PDN conducts, then a low resistance path exists between Out and GND and the output is discharged to GND.

### Que 3.2. What are the properties of dynamic circuit ?

#### Answer

#### The properties of dynamic circuit are :

- 1. Dynamic logic has higher speed than equivalent static family.

- 2. It occupies less area. The number of transistors is lower than in the static case.

- 3. It is non-ratioed. The noise margin does not depend on transistor ratios, as is the case in the pseudo-nMOS family.

- 4. It has low power dissipation. It only consumes dynamic power. No static current path ever exists between  $V_{DD}$  and GND.

- 5. Dynamic logic always require clock.

### Que 3.3. Explain the behavior of pass transistor in dynamic

CMOS logic implementation.

AKTU 2020-21, Marks 07

#### OR

Explain the working of pass transistor circuit. Also explain how the charge stored affects the transfer of logic '1' and logic '0' in nMOS pass transistor circuits.

#### Answer

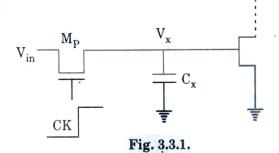

1. The fundamental building block of nMOS dynamic logic circuits consisting of a nMOS pass transistor driving the gate of another nMOS as shown in Fig. 3.3.1.

#### 3-4 F (EC-Sem-7)

2. The pass transistor  $M_P$  is controlled by periodic clock pulse and acts as a switch to charge up or charge down the parasitic capacitance  $C_x$ .

- 3. There are two possible operation when CK = 1, they are logic '1' transfer *i.e.*, charging up the capacitance  $C_x$  and logic '0' transfer *i.e.*, charging down the capacitance  $C_x$ .

- 4. The pass transistor  $M_p$  provides the only current path to the capacitive node (soft node)  $V_x$ .

- 5. When CK = 0, the pass transistor  $M_P$  ceases the path and charge stored in parasitic capacitor  $C_r$  is used to determine the output of the inverter.

#### A. Logic '1' transfer :

- 1. Assume that the soft node voltage is equal to 0 initially, *i.e.*,  $V_x(t=0) = 0$  V. A logic '1' level is applied to the input terminal which corresponds to  $V_{in} = V_{OH} = V_{DD}$ .

- 2. Now the clock signal at the gate of the pass transistor goes from 0 to  $V_{DD}$  at t = 0.

- 3. The pass transistor  $M_P$  starts to conduct as soon as the clock signal becomes active. With  $V_{DS} = V_{GS}$ , the  $M_P$  will operate in saturation region throughout this cycle, since  $V_{DS} > V_{GS} V_{T,n}$ .

#### B. Logic '0' transfer :

- 1. Assume that the soft node voltage  $V_x$  is at logic '1' level initially *i.e.*,  $V_x(t=0) = V_{\max} = (V_{DD} - V_{T,n})$ . A logic '0' level is applied to the input terminal, which corresponds to  $V_{\text{in}} = 0$  V.

- 2. Now the clock signal at the gate of the pass transistor goes from 0 to  $V_{DD}$  at t = 0.

- 3. The pass transistor  $M_p$  starts to conduct as soon as the clock signal becomes active. In this case, the direction of drain current flowing through  $M_p$  will be opposite to that in the logic '1' transfer.

- 4. With  $V_{GS} = V_{DD}$  and  $V_{DS} = V_{max}$ , the pass transistor operates in the linear region throughout this cycle, since  $V_{DS} < V_{GS} V_{T,n}$ .

### Que 3.4. Estimate the equation for the charge storage and charge leakage at the soft node capacitance $C_x$ .

#### VLSI Design

#### 3-5F (EC-Sem-7)

#### Answer

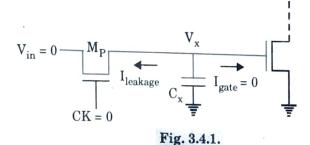

- 1. The preservation of correct logic at soft node during inactive clock pulse depends on sufficient amount of charge in  $C_r$ .

- 2. Let us assume that high logic has been transferred to the soft node during active clock pulse, and both the input voltage  $V_{in}$  and clock are equal to 0 V as shown in Fig. 3.4.1.

- 3. The charge in  $C_x$  will gradually leak away due to leakage currents associated with pass transistor  $M_p$ . The gate current of inverter transistor is negligible.

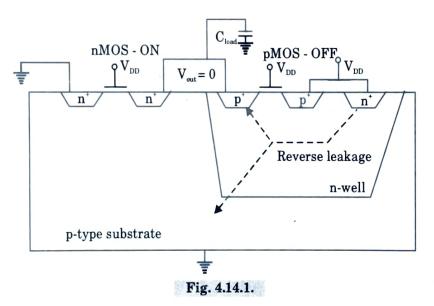

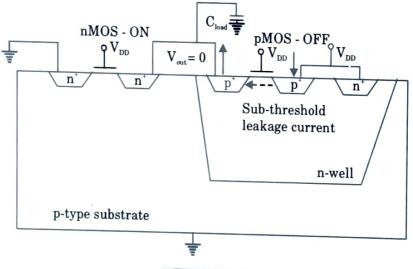

- 4. The leakage current responsible for draining the soft node capacitance over time has two responsible components. They are subthreshold channel current and reverse conduction current.

$$I_{\text{leakage}} = I_{\text{subthreshold }(M^P)} + I_{\text{reverse }(M^P)} \qquad \dots (3.4.1)$$

Other component of  $C_x$ , like oxide related parasitic can be considered constants, and represented by  $C_{in}$ .

5. The sum of two main components are used to express the total charge stored in the soft node

where

m

$$\begin{split} &Q = Q_j(V_x) + Q_{\text{in}} \\ &Q_{\text{in}} = C_{\text{in}} \cdot V_x \\ &C_{\text{in}} = C_{gb} + C_{\text{poly}} + C_{\text{metal}} \end{split} \tag{3.4.2}$$

6. The time derivation of the total soft node charge Q will give the total leakage current as

$$\begin{split} I_{\text{leakage}} &= \frac{dQ}{dt} = \frac{dQ_j(V_x)}{dt} + \frac{dQ_{\text{in}}}{dt} \\ &= \frac{dQ_j(V_x)}{dV_x} + \frac{dV_x}{dt} + C_{\text{in}}\frac{dV_x}{dt} \qquad \dots (3.4.3) \end{split}$$

Que 3.5.

### Explain the term voltage bootstrapping in CMOS logic

#### with suitable example.

AKTU 2018-19, Marks 05

#### Answer

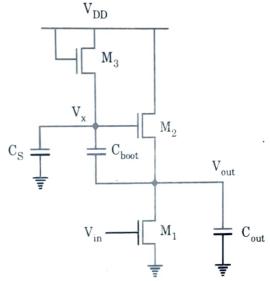

1. Voltage bootstrapping is a very useful dynamic circuit technique for overcoming threshold voltage drops in digital circuits.

#### 3-6 F (EC-Sem-7)

Dynamic CMOS Design

2. Dynamic voltage bootstrapping techniques offer a simple yet effective way to overcome threshold voltage drops which occurs in most situations.

Fig. 3.5.1. Dynamic bootstrapping arrangement to boost V<sub>x</sub> during switching.

3. When input voltage V<sub>in</sub> is low, maximum value of output voltage can be attain, is limited by

$$V_{\text{out}}(\max) = V_r - V_{T2}(V_{\text{out}})$$

...(3.5.1)

- 4. To overcome threshold voltage drop and to obtain full logic high level  $(V_{DD})$  at output node, the voltage  $V_x$  must be increased.

- 5. As shown in figure  $M_3$  is added to circuit. The two capacitors  $C_S$  and  $C_{\text{boot}}$  represent capacitances which dynamically couple voltage  $V_x$  to ground and to output respectively.

- 6. This circuit produces a high  $V_x$  during switching, so that threshold voltage drop is overcome at output.

$$V_x \ge V_{DD} + V_{T2} (V_{out})$$

...(3.5.2)

According to equation,

$$i_{CS} \approx i_{Cboot} \Rightarrow C_S \frac{dV_x}{dt} \approx C_{boot} \frac{d(V_{out} - V_x)}{dt}$$

$$\frac{dV_x}{dt} = \frac{C_{boot}}{C_S + C_{boot}} \cdot \frac{dV_{out}}{dt} \qquad \dots (3.5.3)$$

7. It is seen from equation that increase in output voltage  $V_{out}$  during this switching event will proportionally increase voltage level  $V_x$ . Integrating eq. (3.5.3) on both sides, we get

$$\int_{V_{DD}-V_{T3}}^{V_{x}} dV_{x} = \frac{C_{\text{boot}}}{C_{S}+C_{\text{boot}}} \int_{V_{OL}}^{V_{DD}} dV_{\text{out}}$$

$$V_{x} = (V_{DD}-V_{T3}) + \frac{C_{\text{boot}}}{C_{S}+C_{\text{boot}}} (V_{DD}-V_{OL}) \dots (3.5.4)$$

#### VLSI Design

#### 3-7 F (EC-Sem-7)

8. If capacitor  $C_{\text{boot}} >> C_S$ , maximum value of  $V_x$  is  $V_x(\text{max}) = 2V_{DD} - V_{T3} - V_{OL}$  ...(3.5.4) which proves that voltage bootstrapping can significantly boost the voltage level  $V_x$ .

Que 3.6. Differentiate between dynamic CMOS logic circuit and static CMOS logic circuit.

#### Answer

| S. No. | Parameter            | Static CMOS<br>logic circuit | Dynamic CMOS<br>logic circuit                                                |

|--------|----------------------|------------------------------|------------------------------------------------------------------------------|

| 1.     | Glitches             | 30 % energy increase         | Intrinsically does not<br>have this problem                                  |

| 2.     | Switching activity   | Depends on previous<br>state | Does not depend on previous state.                                           |

| 3.     | Power down<br>models | Effectively used             | Generally, higher activity factor.                                           |

| 4.     | Clock Power          | No clock                     | Not well suited<br>due to gate capacitance<br>of precharge MOS<br>transistor |

### PART-2

Noise Consideration in Dynamic Design, Charge Sharing.

#### **Questions-Answers**

Long Answer Type and Medium Answer Type Questions

### Que 3.7. What are the noise considerations in dynamic design ?

Answer

#### Noise considerations in dynamic design are :

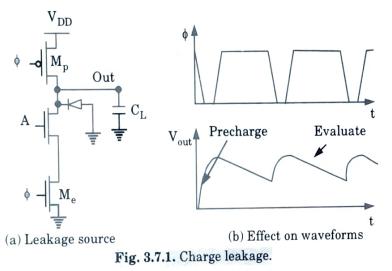

#### i. Charge leakage :

- 1. The operation of the dynamic logic depends on the principles of dynamically storing a charge on the output node (capacitor).

- 2. Due to leakage currents, this charge gradually leaks away, resulting eventually in malfunctioning of the gate.

#### 3-8F (EC-Sem-7)

#### Dynamic CMOS Design

3. Charge leakage causes degradation in the logic high level.

- 4. Dynamic circuits require a minimal clock rate which is typically between 250 Hz and 1 kHz.

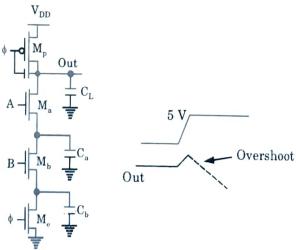

- ii. Charge sharing :

- 1. During the precharge phase, the output node is precharged to  $V_{DD}$ .

Fig. 3.7.2.

- 2. Capacitors  $C_a$  and  $C_b$  represent the parasitic capacitances of the internal nodes of the circuit.

- 3. Assume now that during precharge all inputs are set 0 and the capacitance  $C_a$  is discharged.

- 4. Assume further that input *B* remains at 0 during evaluation, while input *A* makes a 0 to 1 transition.

### VLSI Design

- 5. Turning transistor  $M_a$  ON, the charge stored originally on capacitor  $C_L$  is redistributed over  $C_L$  and  $C_a$ . This causes a drop in the output voltage, which cannot be recovered due to the dynamic nature of the circuit.

- 6. One way of alleviating the problem of charge sharing is to add a small pMOS transistor in parallel with the precharge transistor as shown in Fig. 3.7.3 to supply the extra current needed.

Fig. 3.7.3. Addition of level restoring transistor.

### iii. Clock feed-through :

1. The clock signal is coupled to the storage node by the gate-source capacitance and the gate-overlap capacitance of the precharge device as shown in Fig. 3.7.4.

Fig. 3.7.4. Clock feed through.

- 2. The fast rising and falling edges of the clock couple into the signal node.

- 3. The disadvantage of clock feed-through is that it causes the signal level to rise sufficiently above the supply voltage as to forward bias the junction diode.

#### 3-10 F (EC-Sem-7)

- 4. This causes electron injection into the substrate and eventually resulting in faulty operation.

- 5. This can be avoided by providing a sufficient number of well contacts close to the precharge device to collect the injected current.

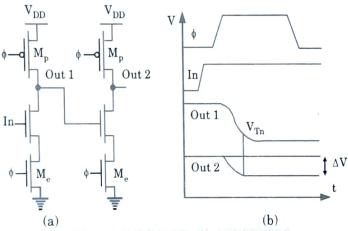

#### iv. Cascading dynamic gate :

1. Cascade dynamic gate is a combination of two simple inverters connected in series, as shown in Fig. 3.7.5.

Fig. 3.7.5. Cascading dynamic gates.

- 2. The problem is that during precharge all outputs are being precharged to 1.

- 3. The PDN of the second gate is thus in a conducting state at the onset of the evaluation phase.

- 4. Suppose now that "In" makes a 0 to 1 transition. At the onset of the evaluation period ( $\phi = 1$ ), output "Out 1" starts to discharge.

- 5. When "Out 1" exceeds the switching threshold of the second gate, a conducting path exists between "Out 2" and GND. "Out 2" therefore discharges as well, and the correct output of the gate equals 1.

- 6. This conducting path is only turned OFF when "Out 1" reaches  $V_{Tn}$  and shuts OFF the nMOS pull-down transistor. This leaves "Out 2" at an intermediate voltage level. The charge loss leads to reduce noise margins and eventual malfunction.

- 7. It is obvious that the cascading problem arise because the output is precharged to "1", so correct operation is guaranteed as long as the inputs can only make a signal 0 to 1 transition during the evaluation period.

### VLSI Design

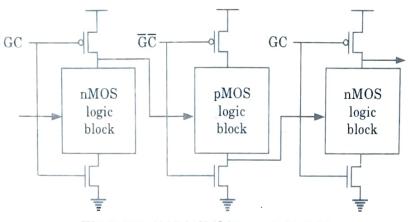

### PART-3

Domino Logic.

**Questions-Answers**

Long Answer Type and Medium Answer Type Questions

Que 3.8. Explain the domino CMOS logic. Also discuss the cascaded domino CMOS logic structures.

OR

Explain CMOS domino circuit along with its features. How it can be